#### THESE DE DOCTORAT DE SORBONNE UNIVERSITE préparée à EURECOM

École doctorale EDITE de Paris n° ED130 Spécialité: «Informatique, Télécommunications et Électronique»

Sujet de la thèse:

## Towards System-Wide Security Analysis of Embedded Systems

Thèse présentée et soutenue à Biot, le 31/07/2020, par NASSIM CORTEGGIANI

| Président    | Prof. Marc Dacier                                                                     | EURECOM                                                                                 |

|--------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Rapporteurs  | Prof. Jean-Louis Lanet<br>Prof. Konrad Rieck                                          | INRIA<br>TU Braunschweig                                                                |

| Examinateurs | Dr. Renaud Pacalet<br>Dr. Marie-Lise Flottes<br>Stéphane Di Vito<br>Nicusor Penisoara | Télécom Paristech<br>Univ. Montpellier / CNRS<br>Maxim Integrated<br>NXP Semiconductors |

|              |                                                                                       |                                                                                         |

Directeur de thèse Prof. Aurélien Francillon EURECOM

## Preface

Even if only my name is written on the cover of this Ph.D. thesis, many people around me deserved credits for its completion. Therefore, I would like to present my grateful to people who have helped for the preparation of this thesis.

First and foremost a special mention to my supervisor, Aurelien Francillon, who has always been helpful, of good advice, and always present for discussions and last-minute reviews.

I would like to thank my collaborators and co-authors. In particular, I would like to thank Giovanni Camurati. Designing and developing the concepts behind this thesis was a huge undertaking that was successful thanks to his precious collaboration.

Then, I would like to thank my colleagues at EURECOM and at Maxim Integrated, for their feedbacks, discussions and cooperation.

I would like to thank the committee members for their time, support, and guidance during the proofreading of this manuscript. Especially, Prof. Jean-Louis Lanet, Prof. Marc Dacier, and Dr. Renaud Pacalet for their extensive feedback on an earlier draft of this manuscript.

Last but not the least, I would like to thank my family for supporting me spiritually throughout the writing of this thesis and my life in general.

This work was supported, in part, by Maxim Integrated and EURE-COM. Any opinions, findings, recommendations or conclusions expressed herein are my own and do not reflect the position or views of any instutition or company.

## Résumé

Les systèmes embarqués sont de plus en plus déployés, comme par exemple les objets connectés ou les systèmes de contrôle critique. Leur sécurité devient une préoccupation importante soit parce qu'ils contrôlent des systèmes sensibles ou parce qu'ils peuvent être exploités pour mettre en oeuvre des attaques à grande échelle.

L'une des spécificités majeures des systèmes embarqués reste les interactions fréquentes entre le micro-logiciel et les périphériques matériels qui font l'interface avec le monde extérieur. Ces interactions sont souvent la source de défauts de conception aussi appelés bugs. Une manière commune de tester ces systèmes est l'analyse dynamique. Cependant, les approches existantes se concentrent généralement sur les logiciels dont les sources ne sont pas disponibles ou testent les composants séparemment les uns des autres comme le code binaire, le code source écrit en C, ou les périphériques matériels. Atteindre l'analyse à l'échelle du système est nécessaire pour tester ces systèmes méticuleusement. Les principaux défis dans ce domaine sont la limitation des performances, les différences sémantiques et le niveau de contrôle/visibilité sur les périphériques matériels.

Dans cette thèse, nous nous attaquons à ces trois défis tout en considérant le point de vue du concepteur. Pour commencer, la thèse offre une discussion générale sur l'analyse de système sur puce à l'échelle du système où nous pointons les défis et soulignons les directions de recherche. Pour palier la limitation des performances lors des interactions avec les périphériques (i.e., test avec le matériel dans la boucle), nous proposons Steroids, une sonde USB3 haute performance. Ensuite, nous avons conçu et développé Inception, une méthode complète pour tester le code-source des micro-logiciels à l'échelle du système. Inception supporte différent niveaux de sémantique (e.g., assembleur et langage C) qui sont souvent combinés lors de la programmation de micro-logiciel. Troisièmement, nous proposons HardSnap une solution pour générer des instantanés de l'ensemble du système testé, incluant aussi bien l'état du matériel que celui du logiciel.

## Abstract

Connected embedded systems are increasingly widely deployed, for example, in IoT devices or critical control systems. Their security is becoming a serious concern, either because they control some sensitive system or because they can be massively exploited to mount large scale attacks.

One of the specificities of embedded systems is the high interactions between the firmware and the hardware peripherals that generally interface them with the real world. These interactions are often the source of critical bugs. One common way of testing such systems is dynamic analysis. However, current approaches generally focus on closed-source firmware and rely on testing components separately such as binary code, C-based code, or hardware peripherals. Achieving system-level testing is necessary to thoroughly test these systems. Major challenges in this topic include performance limitations, semantics differences, and limited control/visibility on hardware peripherals.

In this thesis, we tackle these three main challenges for system-level dynamic analysis of embedded systems while taking the point of view of a designer. To begin with, this thesis offers a general discussion on achieving a system-wide analysis of System-on-Chip (SoC) where we point out challenges and highlight research directions. To overcome performance limitations when interacting with peripherals (i.e., hardware-in-the-loop testing), we propose STEROIDS, a USB3-based high-performance low-latency system probe. Second, we designed and developed INCEPTION, a complete solution for testing system-wide firmware programs source-code. INCEPTION supports different semantics levels (e.g., assembly and C), which are often combined when writing the firmware program. Third, we propose a solution for snapshotting the entire system under test, including both hardware and software *state*. We implement this solution in HARDSNAP, a system that enables system restoration at a precise point for testing multiple execution paths concurrently while preserving analysis consistency.

# Contents

| 1 | Intr        | roduction                                                                                                                  | 1 |

|---|-------------|----------------------------------------------------------------------------------------------------------------------------|---|

|   | 1.1         | Context                                                                                                                    | 3 |

|   | 1.2         | Problem Statement                                                                                                          | 4 |

|   | 1.3         | Thesis Outline                                                                                                             | 4 |

| 2 | Bac         | kground                                                                                                                    | 5 |

|   | 2.1         | Threats and Risks                                                                                                          | 6 |

|   | 2.2         | Embedded Systems                                                                                                           | 7 |

|   |             | 2.2.1 Firmware                                                                                                             | 7 |

|   |             | 2.2.2 Peripherals                                                                                                          | 8 |

|   |             | 2.2.3 Hardware/Software Interactions                                                                                       | 9 |

|   | 2.3         | Static and Dynamic Analysis                                                                                                | 0 |

|   | 2.4         | Binary and Source Analysis                                                                                                 | 1 |

|   | 2.5         | Dynamic Symbolic Execution                                                                                                 | 1 |

|   | 2.6         | Partial-Emulation Testing                                                                                                  | 2 |

|   | 2.7         | Challenges                                                                                                                 | 5 |

|   | 2.8         | Contributions                                                                                                              | 5 |

|   | 2.9         | Publications                                                                                                               | 6 |

| 3 |             | C Security Evaluation: Reflections on Methodology and                                                                      |   |

|   | Too         | ling 1'                                                                                                                    | 7 |

|   | 3.1         | Introduction                                                                                                               | 8 |

|   | 3.2         | Background                                                                                                                 | 9 |

|   |             | 3.2.1 Security evaluation of System-on-Chips (SoCs) and                                                                    |   |

|   |             | their firmware $\ldots \ldots $ | 9 |

|   |             | 3.2.2 Analysis context                                                                                                     | 0 |

|   |             | 3.2.3 SoC and firmware at Hack@DAC19                                                                                       | 0 |

|   | $3 \cdot 3$ | Security evaluation methodology                                                                                            | 1 |

|   |             | 3.3.1 Requirements on tooling                                                                                              | 1 |

|   |             | 3.3.2 Available tools                                                                                                      | 2 |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                   |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|          | ~ .               | 0.01                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                   |

|          | $3 \cdot 4$       |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25<br>- C                                                                                            |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26<br>c                                                                                              |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                                                                                                   |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                                                                   |

|          | 3.5               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                   |

| <b>4</b> | Ster              | roids: A fast, low-latency USB <sub>3</sub> Debugger                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                                                   |

|          | 4.1               |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                                                                   |

|          | 4.2               | Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                           | 31                                                                                                   |

|          | $4 \cdot 3$       | Design Objectives                                                                                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                   |

|          | $4 \cdot 4$       | Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                                                   |

|          | $4 \cdot 5$       | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                                                   |

|          | 4.6               | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                              | 37                                                                                                   |

|          |                   | 4.6.1 Average I/O per Second                                                                                                                                                                                                                                                                                                                                                                                                            | 37                                                                                                   |

|          |                   | 4.6.2 Improvment in Avatar                                                                                                                                                                                                                                                                                                                                                                                                              | 38                                                                                                   |

|          | $4 \cdot 7$       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                                                   |

| 5        | Ince              | eption: System-Wide Security Testing of Real-World                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                      |

|          | $\mathbf{Em}$     | bedded Systems Software                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                   |

|          | $\mathbf{Em}$     |                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>41</b><br>42                                                                                      |

|          |                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                                                   |

|          | 5.1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>46                                                                                             |

|          | 5.1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>46<br>46                                                                                       |

|          | 5.1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>46<br>46<br>47                                                                                 |

|          | 5.1<br>5.2        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>46<br>46<br>47<br>49                                                                           |

|          | 5.1               | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation                                                                                                                                                                                                                                                                            | $42 \\ 46 \\ 47 \\ 47 \\ 51 \\ 51$                                                                   |

|          | 5.1<br>5.2        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>46<br>47<br>49<br>51<br>51                                                                     |

|          | 5.1<br>5.2        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | $42 \\ 46 \\ 47 \\ 51 \\ 51 \\ 52 $                                                                  |

|          | 5.1<br>5.2        | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter                                                                                                                                                                              | $42 \\ 46 \\ 47 \\ 49 \\ 51 \\ 52 \\ 53 $                                                            |

|          | 5.1<br>5.2        | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases                                                                                                                                            | $42 \\ 46 \\ 47 \\ 49 \\ 51 \\ 52 \\ 53 \\ 54$                                                       |

|          | 5.1<br>5.2        | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual Machine5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS                                                                                                                                  | $42 \\ 46 \\ 47 \\ 51 \\ 52 \\ 53 \\ 54 \\ 57 $                                                      |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation                                                                                      | $42 \\ 46 \\ 47 \\ 49 \\ 51 \\ 52 \\ 53 \\ 54 \\ 57 \\ 59$                                           |

|          | 5.1<br>5.2        | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation                                                                                      | $42 \\ 46 \\ 47 \\ 51 \\ 52 \\ 53 \\ 54 \\ 57 \\ 59 \\ 59 $                                          |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation5.4.1Vulnerability detection                                                          | $\begin{array}{r} 42\\ 46\\ 47\\ 51\\ 51\\ 52\\ 53\\ 54\\ 57\\ 59\\ 60\\ \end{array}$                |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation5.4.1Vulnerability detection5.4.2Timing overhead                                      | $42 \\ 46 \\ 47 \\ 51 \\ 52 \\ 53 \\ 57 \\ 59 \\ 60 \\ 63$                                           |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation5.4.1Vulnerability detection5.4.2Timing overhead5.4.3Analysis on real-world code      | $\begin{array}{r} 42\\ 46\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 63\\ 64 \end{array}$                  |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation5.4.1Vulnerability detection5.4.2Timing overhead5.4.4Usage during product development | $42 \\ 46 \\ 47 \\ 51 \\ 52 \\ 53 \\ 57 \\ 59 \\ 60 \\ 63 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67 \\ 67$ |

|          | 5.1<br>5.2<br>5.3 | IntroductionOverview of Inception5.2.1Approach and components5.2.2Lift-and-merge process5.2.3Inception Symbolic Virtual MachineImplementation and validation5.3.1Lift-and-merge process5.3.2Unified Memory Layout5.3.3Application Binary Interface adapter5.3.4Noteworthy control-flow cases5.3.5Forwarding mechanism with STEROIDS5.3.6Validation5.4.1Vulnerability detection5.4.2Timing overhead5.4.4Usage during product development | $\begin{array}{r} 42\\ 46\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 63\\ 64 \end{array}$                  |

| 6  | Har            | dSnap:  | Leveraging Hardware Snapshotting                                                                  | for   | Em   | bed | -         |

|----|----------------|---------|---------------------------------------------------------------------------------------------------|-------|------|-----|-----------|

|    | $\mathbf{ded}$ | System  | ns Security Testing                                                                               |       |      |     | <b>73</b> |

|    | 6.1            | Introdu | $\operatorname{action}$                                                                           |       |      |     | 74        |

|    |                | 6.1.1   | Related Work                                                                                      |       |      |     | 77        |

|    | 6.2            | Motiva  | tion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$             |       |      |     | 80        |

|    | 6.3            | Design  | Objectives                                                                                        |       |      |     | 82        |

|    | 6.4            | Design  | Overview                                                                                          |       |      |     | 83        |

|    |                | 6.4.1   | Peripheral Snapshotting Mechanism                                                                 |       |      |     | 85        |

|    |                | 6.4.2   | Selective Symbolic Virtual Machine                                                                |       |      |     | 86        |

|    |                | 6.4.3   | Snapshotting Controller                                                                           |       |      |     | 88        |

|    | 6.5            | Archite | ecture and Implementation                                                                         |       |      |     | 88        |

|    |                | 6.5.1   | Hardware Snapshotting Instrumentation .                                                           |       |      |     | 88        |

|    |                | 6.5.2   | Selective Symbolic Virtual Machine                                                                |       |      |     | 90        |

|    | 6.6            | Evalua  | $tion \ldots \ldots$ |       |      |     | 91        |

|    |                | 6.6.1   | Experiment I: Hardware Snapshotting Per                                                           | forr  | nanc | e   | 93        |

|    |                | 6.6.2   | Experiment II: Gain for Firmware Analyst                                                          | is To | ools |     | 96        |

|    |                | 6.6.3   | Experiment III: Case Study                                                                        |       |      |     | 99        |

|    | 6.7            | Limitat | $z_{\rm ions}$                                                                                    |       |      |     | 100       |

|    | 6.8            | Conclu  | sion                                                                                              |       |      |     | 100       |

| 7  | Con            | clusion | and Future Work                                                                                   |       |      |     | 103       |

|    | 7.1            | Conclu  | sion                                                                                              |       |      |     | 104       |

|    | 7.2            | Future  | Work                                                                                              |       |      |     | 105       |

| Aŗ | opene          | dices   |                                                                                                   |       |      |     | 107       |

| -  | .1             |         | les of IR level adaptation $\ldots \ldots \ldots$                                                 |       |      |     | 111       |

# List of Figures

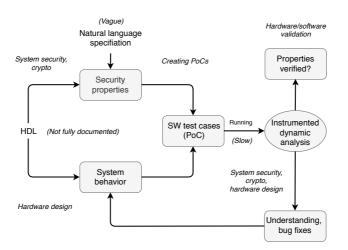

| 3.1                        | Overview of the security evaluation methodology based on<br>dynamic analysis. Manual work and human expertise from<br>different fields are marked in italic                                                      | 24       |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

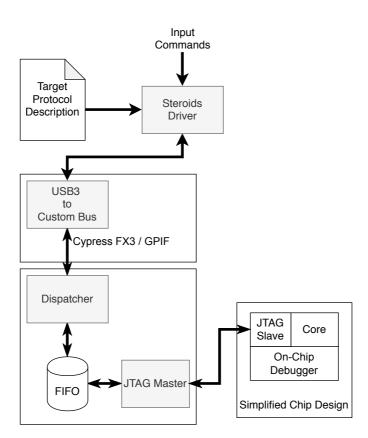

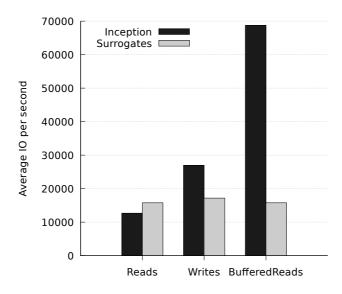

| 4.1<br>4.2                 | Overview of Steroids                                                                                                                                                                                             | 34<br>38 |

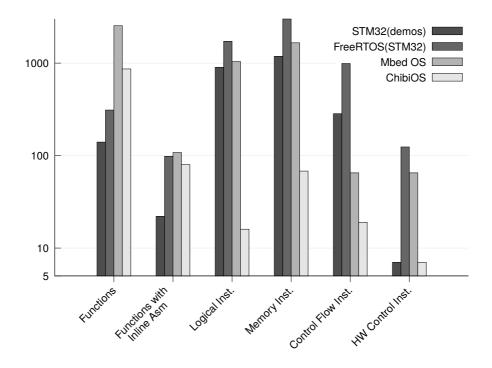

| 5.1                        | Presence of assembly instructions in real-world embedded software                                                                                                                                                | 45       |

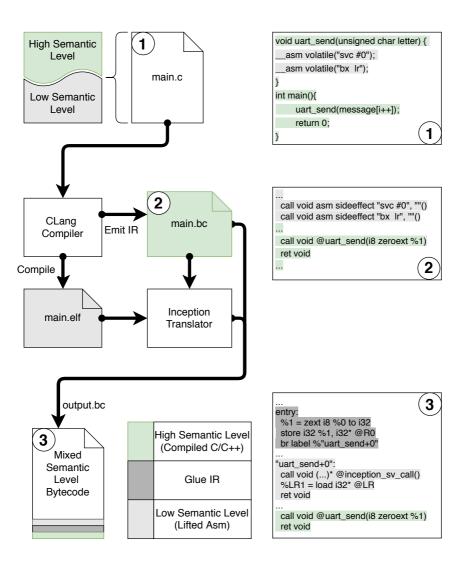

| 5.2                        | Overview of <i>Inception Translator</i> : merging high-level and<br>low-level semantic code to produce mixed semantic bitcode.<br>Excerpt of the translation of a program which includes mixed                   | 45       |

| $5 \cdot 3$                | source and assembly                                                                                                                                                                                              | 48       |

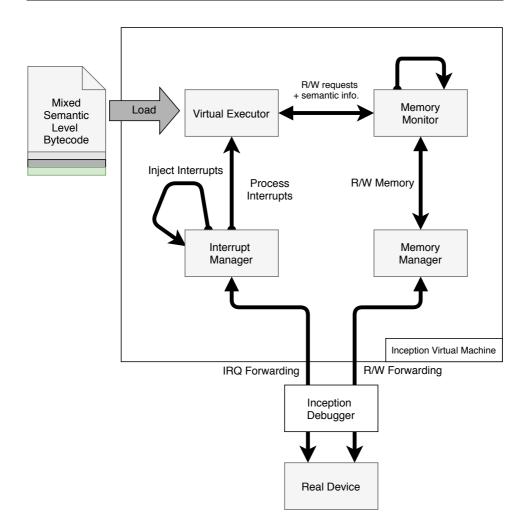

|                            | environment.                                                                                                                                                                                                     | 50       |

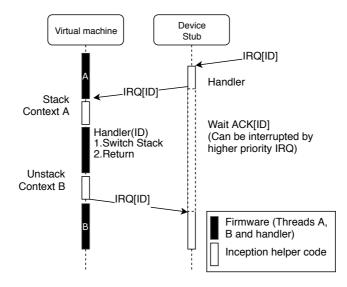

| $5 \cdot 4$<br>$5 \cdot 5$ | Context switch due to an IRQ                                                                                                                                                                                     | 57       |

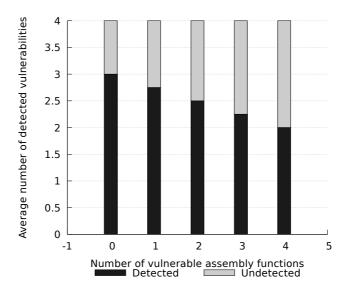

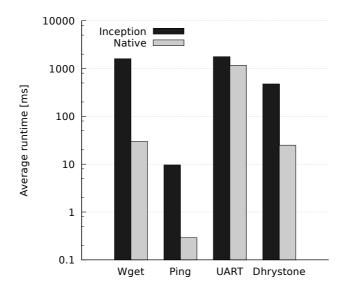

| 5.6                        | symbolic inputs, and a timeout of $9.0 \times 10^1$ s)<br>Performance comparison between native execution and In-<br>ception. (libusb-0.1-4, Ubuntu16.04 LTS, Intel Corporation<br>8 Series/C220 USB Controller) | 63<br>64 |

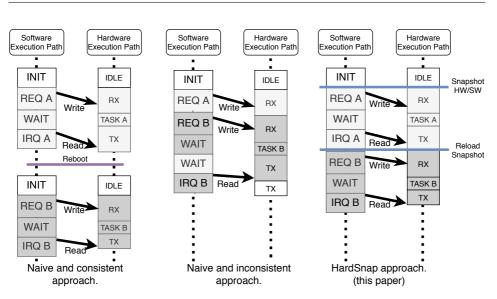

| 6.1                        | Description of different Hardware/Software co-testing execu-<br>tion. From left to right: naive and consistent but slow ap-<br>proach; naive and fast but inconsistent approach, HARDSNAP                        |          |

|                            | approach                                                                                                                                                                                                         | 82       |

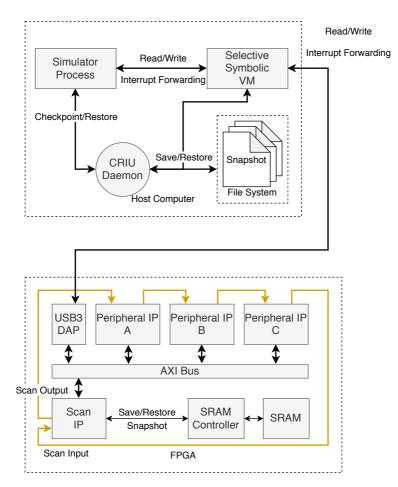

| 6.2 | Overview of HARDSNAP                                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

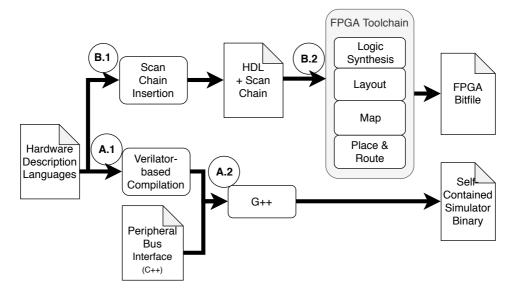

| 6.3 | HARDSNAP's instrumentation toolchain                                                                                                            |

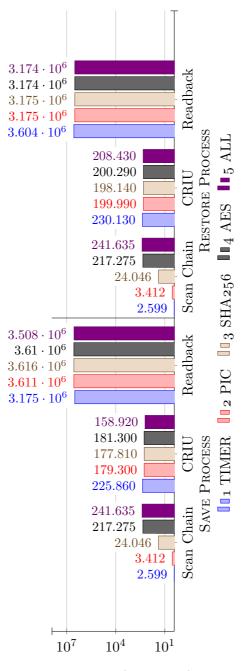

| 6.4 | Average duration, in microseconds, for $10^6$ snapshot saves or                                                                                 |

|     | restores for the FPGA and the simulator. Note the y-axis is                                                                                     |

|     | plotted on a logarithmic scale                                                                                                                  |

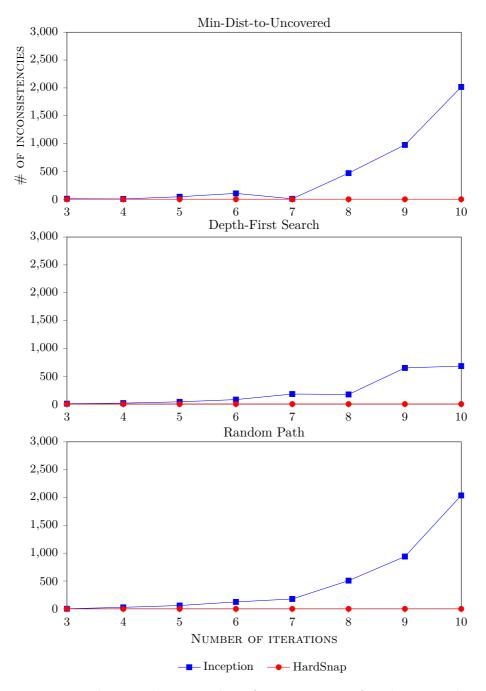

| 6.5 | The cumulative number of inconsistencies found in a syn-                                                                                        |

|     | thetic firmware with different state selection heuristics by the                                                                                |

|     | number of iterations                                                                                                                            |

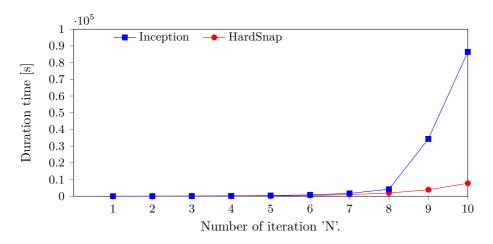

| 6.6 | The duration time by the number of iterations 'N' (Number                                                                                       |

|     | of explored states= $2^N$ )                                                                                                                     |

| 6.7 | Use case written in C to verify the correctness of the PIC                                                                                      |

|     | $peripheral. \ldots 100$ |

|     |                                                                                                                                                 |

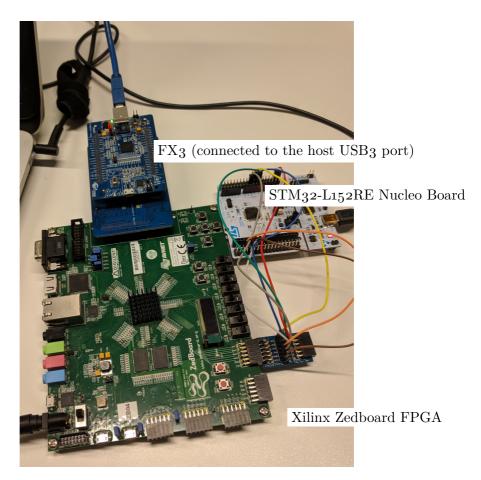

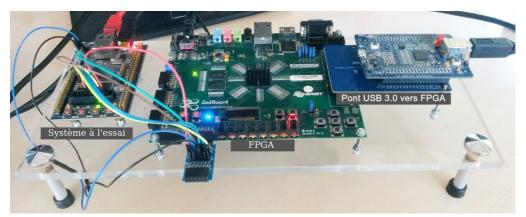

| 1   | Hardware components of the Inception system using an STM <sub>32</sub>                                                                          |

|     | demo board using an Arm Cortex-M3                                                                                                               |

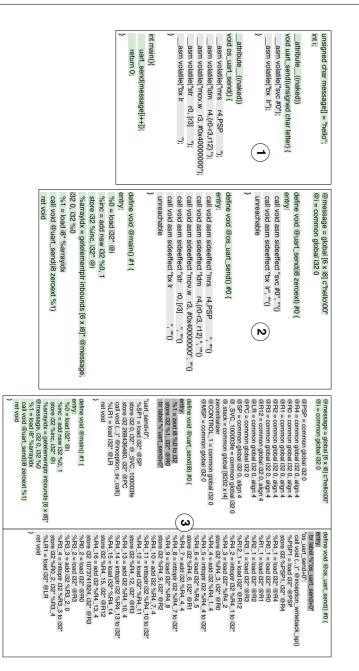

| 2   | Example program with mixed source and assembly. $(1)$ the                                                                                       |

|     | original C source code with inline assembly code. (2) CLang                                                                                     |

|     | generated LLVM bitcode. $(3)$ mixed-IR: LLVM bitcode with                                                                                       |

|     | produced by merging lifted bitcode with CLang generated                                                                                         |

|     | bitcode. We use the naked keyword to limit the size of the                                                                                      |

|     | $example. \ldots 110$                  |

|     |                                                                                                                                                 |

## Glossary

- $\mathbf{SoC}$  System-on-Chip

- $\mathbf{PoC}$  Proof of Concept

- IP Intellectual Property

- I/O Input/Output

- ${\bf SPI}$ Serial Peripheral Interface

- **UART** Universal Asynchronous Receiver-Transmitter

- ${\bf I2C}$  Inter-Integrated Circuit

- IC Integrated Circuit

- ${\bf USB}\,$  Universal Serial Bus

- **DMA** Direct Memory Access

- MMIO Memory Mapped Input/Output

- PMIO Port Mapped Input/Output

- ${\bf DSE}\,$  Dynamic Symbolic Execution

- **BSP** Board Support Package

- ${\bf EGT}$  Execution-Generated Testing

- **ISA** Instruction Set Architecture

- **API** Application Programming Interface

- **RTL** Register-Transfer Level

- **ROM** Read Only Memory

FPGA Field Programmable Gate Arrays

**AES** Advanced Encryption Standard

**SHA** Secure Hash Algorithms

**CPU** Central Processing Unit

**IoT** Internet-of-Things

ICE In-Circuit Emulator

**OCD** On-Chip Debugger

JTAG Joint Test Action Group

**PCI-E** Peripheral Component Interconnect Express

DCC Debug Communication Channel

**IDE** Integrated Environment Development

AHB-AP AMBA High-performance Bus Access Port

${\bf IR}\,$  Intermediate Representation

${\bf ELF}\,$  Executable and Linkable Format

**ABI** Application Binary Interface

**BSS** Block Started by Symbol

ICMP Internet Control Message Protocol

**HTTP** Hypertext Transfer Protocol

**OTP** One Time Programmable

**SRAM** Static Random-Access Memory

**SDK** Software Development Kit

VM Virtual Machine

${\bf HW}~{\rm Hardware}$

${\bf SW}$  Software

HDL Hardware Description Language

- ${\bf SSE}\,$  Selective Symbolic Execution

- ${\bf AXI}$  Advanced eXtensible Interface

- ${\bf PIC}\,$  Programmable Interrupt Controller

Chapter 1 Introduction Computer systems are ever more present in all aspects of our modern life. Some compelling examples of such products are cars, personal computers, home appliances, or smartphones. These systems range from the well-known general-purpose computing devices (e.g., personal computer, smartphone, or server) to purpose-built computing devices, so called embedded system.

Historically, embedded systems have been closely linked to the commodity they embedded. They are designed for specific purposes. For instance, the micro-controller in a washing machine that tunes motors speed up. Embedded systems are also an ubiquitous blocks of general-purpose-computer. They handle interactions with mechanical (e.g., hard drive) or electronic systems (e.g., optical drive, or image sensor).

However, embedded systems are now becoming ever more complex, connected and often attached to the Internet network. This forms the so called "Internet of Things" where today's objects are connected to online services through the Internet network. From connected cars to home appliances, and wearables, there is a considerable number of computer systems that emerge in our lifes. It is difficult to precisely quantify the number of deployed connected devices. However, a reference could be the forecast dataset published by Gartner which tracks connected devices in the following markets: healthcare, smart buildings, smart cities, retail, agriculture, utilities, transportation, manufacturing, automotive. According to Gartner [48], 4.81 billions of connected devices are on the market in august 2019. In addition, it forecasts 5.8 billions of endpoints in 2020 that represents a 21% increase from 2019.

The semiconductor market is growing with tremendous volumes making it attractive but also extremely competitive with short time-to-market. As repeatedly proved by the recent litterature, this strain generally lets little room for testing. In addition, the growing complexity of embedded systems makes security analysis challenging. These systems are very often based on micro-controllers running firmware programs that are often written in programming languages that do not protect from memory corruptions (e.g., C/C++, assembly).

The consequence of a vulnerability can be disastrous. First, embedded systems often control a physical or electrical systems in the real world. An unexpected behavior may cause human harm (e.g., industrial robotic arm) or impact the security of real-world infrastructure (e.g., traffic light system). Second, they may collect personal information issued from sensors or interactions with other connected devices, and therefore may reveal individual private life such as habits, location, interests or even credit card numbers. Third, vulnerable connected devices that interact with each other enabling large scale attacks.

In addition, fixing a vulnerability on embedded systems is not always possible. It is rare to find devices with an automated remote update mechanism enabling security updates. Furthermore, some parts of these systems are hardwired, and it requires hardware replacement to fix bugs. This is the case for any silicon-based hardware components and firmware stored on mask ROM. Fixing these parts requires costly re-fabrication as it involves a new wafer mask set that usually costs more than  $1 \times 10^5$  \$. As a consequence, the economical impact for the manufacturer or product owner can be dramatic and may affect its brand image. One compelling example of such issue is the recent vulnerability discovered in the Nvidia Tegra chips embedded in the Nintendo Switch [80]. This security issue is a memory corruption present in the mask ROM bootloader. Nintendo could only correct this issue in new versions of the console equiped with an updated system on chip. And had no choice other than leaving the vulnerability exploitable in all previously manufactured devices.

### 1.1 Context

In this thesis, we take the point of view of a chip manufacturer who is interested in testing chips before manufacturing. For the sake of clarity, we provide a description of this process. Generally, the design of the core is provided by a third-party (e.g., ARM Architecture). Then, this design is extended with custom and re-utilizable hardware blocks also called IP blocks. These blocks form the hardware peripherals that offer a gate to the real world. The level of customization for these blocks can be important especially for Application-Specific Integrated Circuit (ASIC). In this case, IP blocks are customized to fit specific needs. During the chip development cycle, hardware and software are built concurrently to fit short time-to-market. For this reason, chip manufacturers generally test firmware programs and hardware peripherals separately on an emulation or simulation platform. However, testing components separately is often inefficient for detecting bugs that are due to the interactions of different components such as hardware and firmware. For this reason, performing system-wide testing is crucial but challenging due to the short time-to-market and the lack of dedicated tools.

For all these reasons, there is a need for security testing tools to thoroughly test embedded systems software in pre-production.

## **1.2** Problem Statement

The growing complexity of embedded systems has been possible with the deployment of chip that mixes firmware programs and hardware peripherals. This latter offer either an interface to the real world, accelerated computation or custom functionalities. By analogy, hardware peripherals are what software libraries are for desktop applications. They may have intricate semantics and complex interactions with the firmware. Furthermore, these interactions may be the source of critical bugs that may have dramatic impacts in the real world.

In computer science, previous work highlighted promising perspectives for testing complex systems using dynamic analysis techniques ([39], [93], [98], [53], [101], [87], [58], [31], [90]). Research in this field is hindered by a lack of methods for applying these approaches on embedded systems and even more for source-based analysis. Furthermore, most of those solutions address binary only testing. In particular, they often rely on closed-source only testing and limit the analysis to some components of the systems.

In this thesis, we try to answer this question: How much effort do we need to apply system-wide dynamic analysis to embedded systems while considering the point of view of a chip manifacturer?

## **1.3** Thesis Outline

In Chapter 2 "State-of-the-Art", an overview of the state of the art in the field of the source-based security analysis of embedded systems is presented; in Chapter 3 "SoC Security Evaluation: Reflections on Methodology and Tooling" we present a reflection on security analysis of embedded systems, and we point out the main challenges that we seek to tackle in this thesis; in Chapter 4 "Steroids", a fast probe for optimizing existing dynamic security analysis approaches; the work presented in Chapter 5 "Inception: System-Wide Security Testing of Real-World Embedded Systems Software" illustrates a novel approach to support real-world firmware program analysis where in practice different semantics levels are mixed (e.g., inline assembly, C/C++ and binary code); in Chapter 6 "HardSnap: Leveraging Hardware Snapshotting for Embedded Systems Security Testing", we present a technique for snapshotting both firmware and hardware peripherals to enable advanced dynamic analysis techniques without inconsistencies and with performance in mind.

The thesis ends in Chapter 7 with the conclusions and future perspectives. Chapter 2 Background This chapter describes the background relevant to this thesis. To begin with, we detail the threats and the risks that computing systems and more specifically embedded systems face. Then, we define and explain what are embedded systems and how they differ from the traditional desktop computer. Thereafter, we discuss computer testing methods in general and what challenges to overcome when applying these methods to embedded systems. Finally, we present the state of the art on dynamic embedded systems source-code analysis.

## 2.1 Threats and Risks

Nowadays, computer systems are ever more present in all aspects of our modern life. The increasing complexity and connectivity make them more exposed to attacks. After 40 years of history, the main fundamental root cause of attacks remains memory corruption in software programs. The recent MITRE [67] study shows up memory corruptions among the 3 most widespread and critical weaknesses in software. According to [84], 50% of discovered security bugs in GOOGLE CHROME, a popular web-browser written in C/C++, are memory corruptions (i.e., use-after-free, buffer overflow, uninitialized memory). Even if memory-safe languages are available, memory-unsafe languages such as C remains very popular. For instance, the C-language is commonly used for programming software such as Operating Systems (e.g., Linux, Windows, Mac OS, or Android) or payment systems. Exploiting memory corruptions may lead to private information theft, physical infrastructure outage (e.g., bank, health emergency systems), real-world damage (e.g., traffic lights, robotic arms).

Embedded systems are no exception ([10], [11], [12], [13]). Firmware programs are often written with low-level programming languages (e.g., C, C++, assembly) to handle low-level interactions with the hardware. These languages lack memory safety mechanisms (e.g., types checking) and therefore, they frequently lead to memory corruptions. Although memory safe languages have been used in the past for safety-critical systems ([92]) and have been gaining popularity recently ([57, 43, 20, 23]). An overwhelming part of the development of embedded systems is done as a mix of assembly and C.

The consequences of such vulnerabilities can be disastrous. Since embedded systems may drive mechanical systems in the real world, they may cause human harm or damage physical infrastructures. For instance, the Stuxnet [60] worm caused substantial damage to the nuclear program of Iran. Vulnerability may also lead to considerable economic losses for the chip manufacturer, especially when fixing the vulnerability requires costly re-fabrication [80].

There is therefore an important need for security testing tools to automatically detect memory corruptions on firmware programs before production.

### **2.2** Embedded Systems

Embedded systems are now as ubiquitous as the traditional personal computer. The high spread of these systems is tightly coupled with the deployment of micro-controllers. These computer systems reduce the size, cost, and power-consumption of design by embedding all the necessary components to fulfill specific needs inside a single chip. The latter is also referred to as a System-on-Chip. This approach differs from the traditional microprocessor that depends on other external components to run (e.g., memory, motherboard, Graphics Processing Unit) and is designed for genereral purpose.

Embedded systems are heterogeneous systems with a wide variety of architecture where the following components are generally customized: the computer architecture bit widths, the presence of a data/instruction cache, the Instruction Set Architecture, the peripherals, the memory protection mechanisms, the memory size/type, the presence of a co-processor. In the following, we present the two common key components of chip that are mixed together to achieve specific tasks.

#### 2.2.1 Firmware

Embedded systems are often software-driven and combine hardware peripherals and firmware programs. They are often purpose-built computers and therefore involve a high level of customization for both software and hardware. These systems may run a variety of software that can be divided into three categories. We follow the classification from [70] where authors identify three main classes of firmware in embedded devices.

• General-Purpose Operating Systems. These operating systems are designed for versatility, and they can, therefore, address a large variety of applications. Some prominent examples of general-purpose OSs are Linux-based OSs such as Debian [1], Fedora [2], and Arch-Linux [3]. Linux is well-spread because of its free-cost and customization capability. However, such complex OSs generally requires important resources such as memory, CPU time and power-consumption.

Therefore, they are reserved to a powerful category of embedded devices. Such operating systems introduce an abstraction layer making running applications independent from the underlying hardware, and they offer a testing environment relatively similar to desktop programs.

- Embedded Systems Operating Systems. To address time/space constraints, custom operating systems have been developed (e.g. VX-WORKS [91], QNX [24], FREERTOS [21]). Generally, these systems provide an isolation layer between user-space and kernel space thanks to a Memory Protection Unit (MPU) or a logical separation (i.e., context switching). Commonly, embedded devices have the kernel code and the applications code together in a monolithic block [94].

- Bare-metal Firmware. It is also common to find firmware programs running in bare-metal without any Operating System. This approach fits well when the firmware programs have strong time constraints or space constraints. It is generally the case for boot-loader that aims at high performance and low-memory footprint.

#### 2.2.2 Peripherals

To meet specific requirements, system-on-chip blend software and hardware peripherals together. Such peripherals are predesigned digital circuits, often referred to as Intellectual Property (IP) blocks, acquired from internal sources or from third parties. Generally, a peripheral can be intern to the chip or extern, in this case, the communication with an external peripheral passes by a bus generally driven by an internal peripheral (e.g., SPI, I2C, UART). There is a large number of IP, however, they are generally designed for one of these three purposes.

- Hardware Accelerator. For performance and security purposes, algorithms may be implemented using digital circuits. This solution offers higher performance than full-software stack and it enables the algorithm to be separated from the rest of the machine. This is generally the case for cryptographic blocks to avoid any leakage to the software.

- Hardware Input/Output Peripherals. Peripherals are often a gate to the real world where they sample information from sensors or interact with actuators. Some compelling examples are temperature sensors, gyroscopes, proximity sensors, and buttons. I/O peripherals

may also offer a communication interface to drive external peripherals (e.g., SPI, I2C, UART) or transfer data to another device (e.g., USB, Bluetooth, or WiFi).

• Hardware Assisted Features. Finally, peripherals can be classified as hardware support to software to optimize repeated operations (e.g., Direct Memory Access), or to enable event-based programming (e.g., interrupt controller).

### 2.2.3 Hardware/Software Interactions

Generally, firmware programs are interrupt-driven and interact with the underlying hardware through different mechanisms. These interactions are frequent, numerous and somewhat complex. In fact, peripherals may affect the system's memory (i.e., change the data-flow) and interrupt the firmware execution (i.e., change the control-flow). Therefore, testing firmware programs involves a clear understanding and consideration for these interactions. In the following, we describe such mechanisms.

- Interrupt Signal. Firmware programs are event-driven software where execution is frequently interrupted by interrupt signals emitted by peripherals. These asynchronous signals notify the software that a specific task is done. This concept is largely present in embedded systems to reduce the power consumption (an inefficient alternative would be polling) and to fit relatively strong time constraints for some specific tasks.

- Memory Mapped Input/Output (MMIO). A common way for the firmware to drive peripherals is to expose some registers to the firmware address space. This mapped memory enables the firmware to directly interact with internal peripherals.

- **Port Mapped Input/Output (PMIO).** An alternative to the MMIO is the use of dedicated instructions enabling data transfer to peripherals registers through the processor.

- Direct Memory Access (DMA). One specific case of interaction is the Direct Memory Access that is extremely prevalent in embedded systems. It enables firmware/hardware to initiate a transfer of memory chunks between RAM and peripherals' memory or the opposite. It is often implemented by peripherals that require large data transfer such as Ethernet, or WiFi cards.

## 2.3 Static and Dynamic Analysis

Over the years, many security analysis techniques have been proposed. These approaches can be divided into static and dynamic analyses.

Static analysis examines the computer program code without actually executing it. It is possible to achieve a sound analysis. Sound means that giving an expression the analyzer is able to verify that it is always true. In other words, if the analysis claims that an expression X is true then it is actually true. However, in practice such tools often approximate the tested program environment, and are therefore often not complete in the sense that they may report false positives, i.e., a violation that would never happen in reality. In fact, completeness is such that if an expression X is true, the analysis claims that X is true. However, static analysis is often used as a context insensitive method, and is therefore often imprecise. In particular, the program environment is generally modeled using an over-approximation that significantly increases the false positive rate. Some values may not be possible when executing the program under test.

On the contrary, the dynamic analysis methods execute the program concretely in order to limit the execution to realistic values (i.e., context sentitive approach). In fact, the tested program often interacts with its real environment during the analysis. One of the most widely-deployed dynamic analysis technique is certainly fuzzing. The term 'fuzz' was introduced in 1990 by Milleret et al. [66]. Fuzzing runs a test program in a loop while feeding this program with different grammatically or syntactically malformed inputs at each iteration. Intuitively, the efficiency of fuzzing relies on the quality of the test inputs. These inputs exercise part of the code and therefore affect the code-coverage and the accuracy of the vulnerability detection. Generating relevant test cases is challenging. One hindering factor is the presence of complex control-flow (e.g., hashing functions on program inputs) that requires a program inspection to explore the state space of the program systematically. This systematic exploration of the program under test is achieved by a technique called Dynamic Symbolic Execution (DSE) [29] that basically reasons about the program execution to determine which inputs cause which part of the program to be executed. For the sake of clarity, we detail this technique later on. Before going further, we discuss the analysis context and how it affects results.

## 2.4 Binary and Source Analysis

The context under which the security analysis is performed varies a lot. Many approaches base their analysis on binary code ([98], [69], [33], [22], [90], [87], [53], [58], [101]). We emphasize the fact that in the wild many firmware programs are only available in binary form. This approach is generally performed by third parties (e.g., audit, pentesters). However, during the compilation process, most of the source-code semantics, which is crucial for detecting bugs, is gone. This makes binary code analysis more challenging. On the contrary, when the source code is available, the analysis benefits from the availability of high-level semantics (e.g., the types of variables). This semantics information highly simplifies the detection of memory corruptions. There are very few tools for source-based analysis and even less for embedded systems ([39], [93]). Furthermore, the analysis of firmware source-code is not straightforward. In fact, firmware programs are often a mix between high-level programming languages (e.g., C/C++) and low-level programming languages (e.g., inline assembly) to handle interactions with the underlying hardware. In addition, it is common to find binary dependencies (e.g., Board Support Package). Existing firmware source-based analysis approaches either replace unsupported low-level code with handwritten code [39] or stop their analysis when executing low-level code [27].

## 2.5 Dynamic Symbolic Execution

Symbolic execution has been first introduced by J. C. King et al. [56]. This technique is recently getting more popular due to the recent progress on constraint solving. Symbolic execution automatically discovers which inputs cause which parts of the program to be executed. As the name suggests, this technique replaces concrete input values by symbolic input expressions. As a result, the program execution outputs expressions as a function of these symbolic inputs. These expressions are solved by a constraint solver that generates concrete test cases.

Originally, symbolic execution was a static code examination where the analyzer maps symbolic expressions for each variable [29]. However, this approach has two main limitations. First, the programs may generate expressions that cannot be solved by the constraint solver. Second, it fails at handling interactions with external functions. These two problems are alleviated by dynamic analysis techniques such as Execution-Generated Testing introduced by [28] and followed by [27]. EGT executes the program oper-

ations just like the original program and performs symbolic computation only when one of the operands is symbolic. This reduces considerably the size of the symbolic expressions and enables the computation of non-linear arithmetic that would be difficult or expensive in a symbolic form. Furthermore, EGT supports interactions with external functions by using the concrete form.

In software testing, symbolic execution offers a high code coverage but often suffers from the well-known path explosion. In fact, the number of execution paths grows exponentially with the program size (i.e., conditional branch instructions). This is exacerbated when the firmware environment is abstracted ([39]). In particular, peripheral can be treated as a stateless untrusted function where writes are ignored and reads return unconstrained symbolic values. However, this leads to the explosion of the number of possible paths and consider paths that are not actually feasible with the real peripherals (false positives). Different strategies have been proposed to limit this problem. Among them, Partial-Emulation that we present below.

## 2.6 Partial-Emulation Testing

Firmware programs are often designed to run in a resources-limited environment where time and size constraints are consequent. Furthermore, low-power micro-controllers generally lack virtualization and memory isolation making fault detection extremely difficult when running the program on the real device [71]. To overcome this problem, recent work proposed emulation ([52], [72], [31]). The firmware program is executed in a virtual machine that is composed of an Instruction Set Architecture (ISA) emulator and behavioral models for peripherals. This virtual-machine offers higher introspection (i.e., visibility and control) on the firmware. However, peripherals may have intricate semantic making a behavioral model difficult to write and error-prone. Furthermore, the interactions between firmware and peripherals are essential for the analysis as vulnerabilities may source from the specific interaction between firmware and hardware. In fact, the interactions between firmware and hardware are numerous and frequent. These interactions affect both firmware and hardware control-flow. A general approach to this problem is partial-emulation. This method has been first introduced by Avatar [98] and followed by [58] [93] [90] and consists in re-hosting the firmware execution in a virtual machine while forwarding interactions to the real device. In particular, when the firmware program accesses memory-mapped addresses, Inputs/Outputs are seamlessly forwarded to the real device through a debugger. This method reduces the complexity of the analysis at the price of completeness. However, in practice, the latency introduced by the I/O forwarding is generally too important and affects significantly the analysis performance.

| Firmadyne   |      | 31]                                 | GPOS          | n/a             | ×                        | ×                  | ×                 |                 |             |                     | ×                        |                      |                 |             |

|-------------|------|-------------------------------------|---------------|-----------------|--------------------------|--------------------|-------------------|-----------------|-------------|---------------------|--------------------------|----------------------|-----------------|-------------|

| 1 IIIIIIIII |      |                                     | GPOS (        |                 |                          |                    |                   |                 |             |                     |                          |                      |                 |             |

| FIRMALICE   | -    | [87]                                |               | n/a             | ×                        | >                  | ×                 | >               | >           | н                   | ×                        | >                    | >               | >           |

| Firm-afl    | 2019 | $\begin{bmatrix} 101 \end{bmatrix}$ | GPOS          | n/a             | ×                        | ×                  | ×                 | >               | >           | s                   | ×                        | >                    | >               | >           |

| Charm       | 2018 | [93]                                | $_{\rm BM}$   | >               | >                        | ×                  | >                 | ×               | ×           | s                   | ×                        | ×                    | ×               | >           |

| Avatar2     | 2018 | [69]                                | BM/ESOS       | >               | ~                        | •                  | ×                 | ×               | >           | S                   | ×                        | ×                    | ×               | >           |

| FIRMUSB     | 2017 | [53]                                | BM            | ×               | ×                        | >                  | ×                 | ×               | >           | Ι                   | n/a                      | ×                    | ×               | >           |

| Prospect    | 2014 | [00]                                | GPOS          | >               | >                        | ×                  | ×                 | ×               | >           | $\mathbf{v}$        | n/a                      | ×                    | ×               | >           |

| Surrogates  | 2014 | [58]                                | BM/ESOS       | >               | >                        | ×                  | ×                 | ×               | >           | s                   | n/a                      | ×                    | ×               | ×           |

| Avatar      | 2014 | [98]                                | BM/ESOS       | ×               | >                        | `                  | ×                 | ×               | >           | s                   | ×                        | ×                    | ×               | `           |

| FIE         | 2013 | [39]                                | BM            | ×               | ×                        | >                  | >                 | ×               | ×           | Ι                   | n/a                      | >                    | >               | >           |

|             |      |                                     | Firmware Type | Fast Forwarding | Can use real peripherals | Symbolic Execution | Using source code | Inline assembly | Binary code | Context Sensitivity | Ensure HW/SW Consistency | Full Controllability | Full Visibility | Open-source |

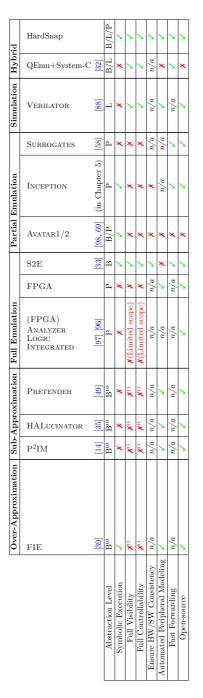

Table 2.1: Related work comparison. BM: Barre Metal; ESOS: Embedded Systems Operating System; GPOS: General Purpose Operating System. Context Sensitivity: Insensitive; Sensitive

## 2.7 Challenges

In the previous part, our literature review points out that modern software testing approaches merely focus on testing desktop applications. Few methods are designed for specifically testing the security of embedded systems and even less for system-wide or source-based analysis. In this thesis, we identify and tackle the three main challenges for applying modern dynamic analysis methods to embedded systems. For the sake of clarity, we present a comparison of existing firmware analysis techniques in Table 2.1. The comparison of previous work highlights fundamental challenges that narrow the dynamic analysis of firmware programs.

Low latency dynamic analysis for embedded systems. Partialemulation is commonly used for testing firmware programs. This technique runs the firmware to test in a controlled environment such as an emulator. However, we showed that hardware and firmware have complex interactions that are difficult to abstract. For this reason, partial-emulation techniques generally forward I/O to the real peripherals using a remote debugger. However, this communication is generally extremely slow making the analysis impractical.

Firmware source-code semantic differences. Most existing techniques focus on analyzing either binary code or source code but neither considers realistic cases where the source-code contains inline assembly or depends on closed-source binary libraries (e.g., Board Support Package). In fact, as we will show in our study in Chapter 5, real-world programs often mix C/C++ and inline assembly to interact with the underlying hardware. Designing a hybrid analysis technique (i.e., binary and source together) is necessary for achieving a system-wide analysis of real-world programs.

**Controlling/observing both firmware/hardware peripherals.** Generally, testing embedded systems involves a full-control and full-visibility over the system under test. This enables to inspect the internal state of the system in order to detect design flaw. However, achieving this level of introspection is challenging for embedded systems that mix firmware and peripherals. Existing methods face a trade-off between performance and visibility/control.

### 2.8 Contributions

In this thesis, we tackle the main challenges research face to apply modern source code security analysis techniques to embedded systems software. In particular, we make the following contributions:

- A reflection on System-on-Chip dynamic analysis where we point out challenges and possible research directions.

- Steroids, a low-latency and high performance USB3-based Debugger. Our solution overcomes the current performance limitation of dynamic analysis techniques where the interactions with hardware pass through a debugger device.

- Inception, a novel framework for system-wide dynamic analysis of firmware programs. This tool is the first dynamic symbolic execution engine that fully supports the security analysis of firmware programs source code. We analyzed different widespread firmware programs and observed that even when the source code is available, it is often a mix of different programming languages having different semantics levels.

- HardSnap a technique for both hardware/software snapshots. This novel method is relevant for many embedded systems dynamic analysis tools that require system-level state manipulation. We implemented this method on top of Inception and demonstrate the performance enhancement during analysis. Furthermore, we identify and explain possible inconsistencies when HardSnap is not enabled.

## 2.9 Publications

This thesis has led to three publications.